## 2. Any revealing of identification, appeal to evaluator and /or equations written eg, 42+8 = 50, will be treated as malpractice. Important Note: 1. On completing your answers, compulsorily draw diagonal cross lines on the remaining blank pages.

**USN**

## Fifth Semester B.E. Degree Examination, December 2011 **Fundamental of CMOS VLSI**

Time: 3 hrs.

Max. Marks:100

Note: Answer any FIVE full questions, selecting at least TWO questions from each part.

## PART - A

- a. Explain the nMOS enhancement mode transistor for different conditions of v<sub>ds</sub>. (08 Marks) (08 Marks)

- b. Describe in detail BiCMOS fabrication in an n-well process. c. What are the advantages of BiCMOS process over CMOS technology?

(04 Marks)

a. What is body effect? Which parameters are responsible for it?

(08 Marks)

b. An nMOS transistor is operating in active region with following parameters  $V_{GS} = 3.9V$ ,

$V_{th}$  = 1V ,  $\frac{W}{\tau}$  =100 ,  $\mu_n$   $c_{ox}$  = 90  $\mu A/r^2.$  Find  $I_D$  and drain to source resistance. (05 Marks)

c. Explain in detail regions of operation and mid-point voltage equation for CMOS inverter.

(07 Marks)

a. List the  $\lambda$ -based design rules for CMOS.

(05 Marks)

b. Draw the stick diagram for nMOS EX-OR gate.

(07 Marks)

c. What is transmission gate? And design stick diagram for transmission gate.

(08 Marks)

What is clocked CMOS gate? Where it is preferred? 4

(06 Marks)

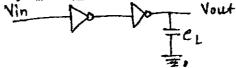

Two nMOS inverters are cascaded to drive capacitive load C<sub>L</sub> = 16 C<sub>g</sub> as shown in Fig.Q.4(b). Calculate pair delay  $v_{in}$  to  $v_{out}$  interms of  $\tau$ . (06 Marks)

Fig.Q.4(b)

- Find the scaling factors for MOS circuits:

- For gate capacitance i)

ii) Channel resistance (Ron)

- Saturation current (Id<sub>ss</sub>) ; ii)

- iv) Speed power product (PT).

(08 Marks)

## PART - B

Design bus arbitration logic for n-line bus. 5 a.

(10 Marks)

Explain two-phase clocking generator using D flip - flops. b.

(10 Marks)

Explain the design steps for 4 bit adder.

(08 Marks)

Draw the basic arrangements of 4 bit serial parallel multiplier. b.

(08 Marks)

c. Discuss the timing constraints for system timing considerations.

(04 Marks)

- a. For single phase clock define following parameters:

- Set up time  $(T_s)$ ; ii) Hold time  $(T_n)$ ; iii) Clock to Q delay  $(T_q)$ .

(03 Marks) (09 Marks)

b. How to read or write and hold the bit in SRAM cell?

- Explain the working of 1-transistor DRAM cell. Give the difference between SRAM and (08 Marks) DRAM.

- a. Discuss the meaning of "REAL ESTATE" in VLSI design. 8

(04 Marks)

What are the different types of I/O pads? b.

(06 Marks)

List the ground rules for a system design.

(10 Marks)

\* \* \* \* \*